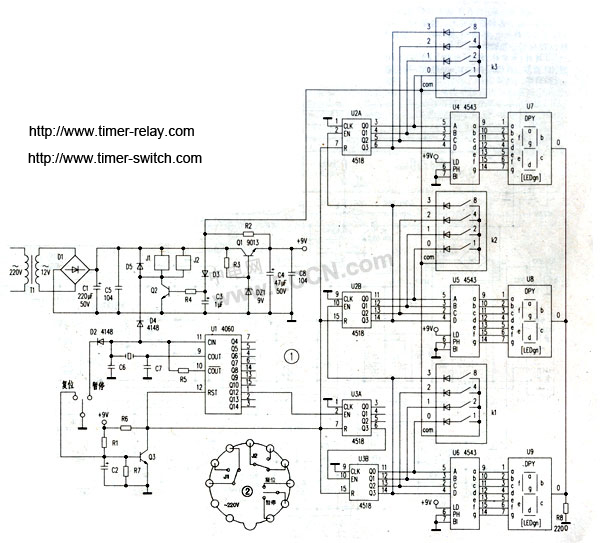

JS14S 数显时间继电器原理图

一、JS14S数显时间继电器使用的集成电路简介

1.十四阶BIN计数及分配器4060BP其圈12脚RST为电路复位控制(高电平有效);

11脚为振荡器时钟输入端;

⑨脚为振荡电容接入COUT;

⑩脚Rtc为振荡电阻接入COUT;

振荡频率f≈1/2.3Rtc×Ctc;Q3~Q9,Q11-Q13为分频计数输出。

2.JS14S数显时间继电器用双BCD计数器/4518BE⑦、圈15⑩脚Mra、MRb分别为两个BCD计数器的复位控制端R;①、⑨脚CPoa、CPob为时钟上升沿计数输入端CLK;②、⑩脚CP1a、CP1b为时钟下降沿计数输入 端EN;Qoa ~Q3a,Qob ~Q3b为BCD码计数输出Q0~Q3。

3.七段译码驱动CD4543BEA、B、C、D为BCD码输入端;PH为状态输入(高电平有效);BI为消隐输入(高电平有效);LD为锁存无效控制(高电平有效);a~g为七段数码管驱动输出。

二、电路剖析220V交流电经降压、整流,C1、C5滤波,输出12V直流,为继电器J1、J2供电;12V直流电压又经Q1、R3、DZl、C4、C8稳压,输出9V直流电为整个电路供电。R1、C2、R6、R7、Q3构成复位电路,上电后由03集电极输出复位脉冲将U1、U2、U3复位。40.690kHz晶振构成的振荡器经4060BP十二分频从①脚输出周期为0.1秒的计数脉冲,送入U3a(4518)②脚(下降沿计数),进行十进制计数,从⑥脚送出周期为1秒的计数脉冲送入U3b⑩脚(下降沿计数),从圈11、圈12、圈14脚输出:BCD计数码至K1(BCD码拨号开关)及U6(4543),驱动数码管U9(个位)显示计数:同时U3b圈14脚输出的BCD码最高位(周期为10秒)送入U2b⑩脚作为十位的计数脉冲。同样U2b⑩脚输出的:BCD码最高位(周期为100秒)送入U2a②脚作为百位的计数脉冲。从图1中可以看出.BCD码拨号开关K1、K2、K3内部的二极管阵列与个、十、百计时位的:BCD码输出端并联,其公共端COM接于二极管D3正端。只有当个、十、百计时位的BCD码输出端与BCD码拨号开关K1、K2、K3的预设BCD码(即预设时间)相同时,D3正端才能输出高电平,驱动Q2导通,使J1、J2吸合。否则。D3正端被钳位于低电平.Q2不能导通。Q2导通后,U111脚经D4被拉于低电平.振荡器停振,计时被锁定于预设时间。此时,若时间继电器复位端对地短接一下.则Q3集电极将输出复位脉冲,使U1、U2、U3复位,计时再次从零开始。若在计时过程中,时间继电器暂停端对地短接,则U1圈11脚经D2被拉于低电平,振荡器停振,计时暂停,断开暂停端计时继续。

因晶振为40.690kHz故此款时间继电器计时范围为0~999秒。

图2为该时间继电器的插脚接线图。

在线客服1

在线客服1 陶宝客服

陶宝客服